1. CDADIC Project: Low-Noise Multiple-Output Switched-Capacitor Power Management System for SoC

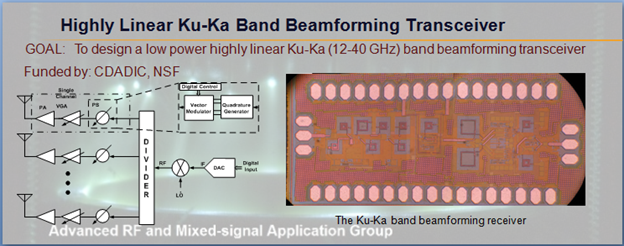

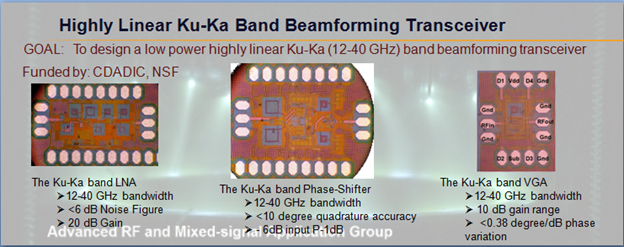

2. A Ku-Ka Band Single Channel Beamforming Receiver

The research objective of this paper is to investigate high performance MMICs for ultra wideband, highly linear beamformer chipsets for phased array communication systems from Ku to Ka bands, which cover the operating frequency ranges of satellite communications, and terrestrial microwave communications. Based on scaled silicon-based technologies, key sub-blocks, including wideband low noise amplifiers, wideband variable gain amplifiers with reduced phase error, and an active phase shifter has been implemented.

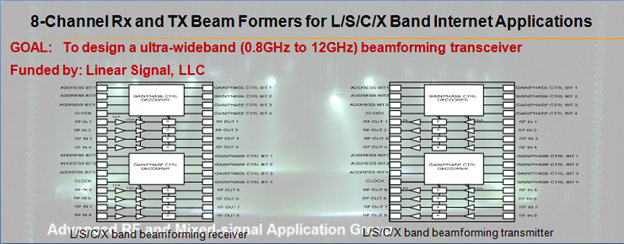

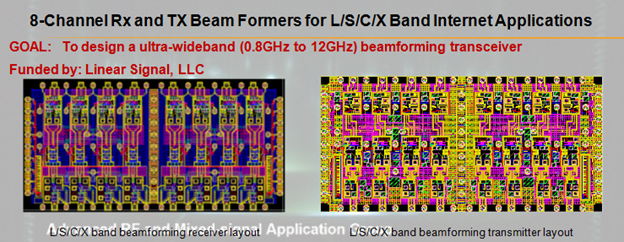

3. 8-Channel Rx and TX Beam Formers for L/S/C/X Band Internet Applications

The goal of this project is to develop compact, wideband, 8-channel receiver and transmitter beam formers for L/S/C/X band internet applications. Two beam formers (8-channel receiver and 8-channel transmitter) have been developed.

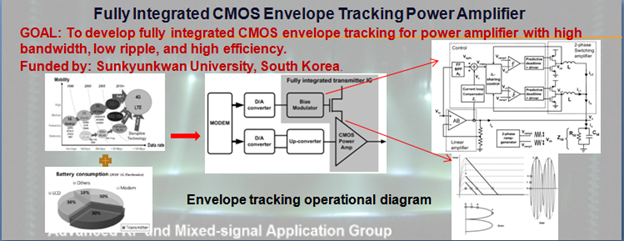

4. Fully Integrated CMOS Envelope Tracking Power Amplifier

The objective of this research is to design a fully integrated CMOS envelop tracking power amplifier integrated circuit for mobile terminals for the next generation of wireless communication applications. This research includes the design of high efficiency and wide bandwidth envelope tracking modulator circuits and fully integrated linear CMOS power amplifiers on the same chip for both high performance and low cost solution.

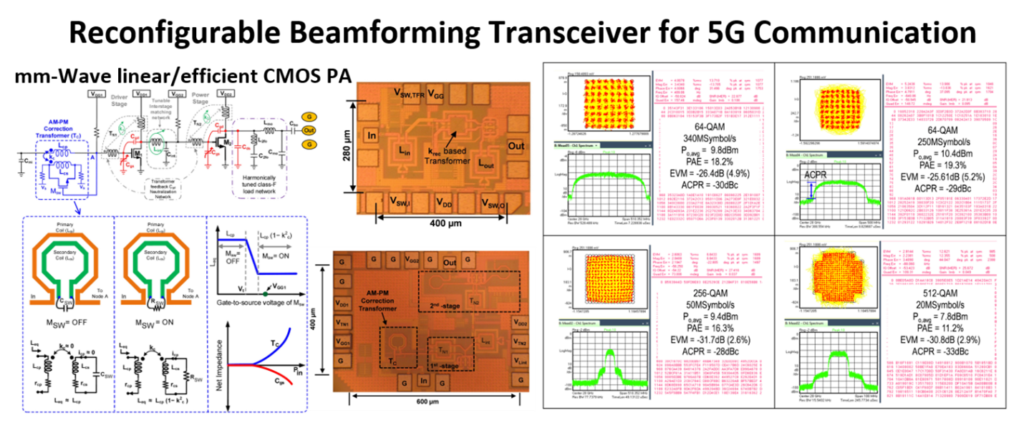

5. Reconfigurable Beamforming Transceiver

Insatiable demand for higher data rates together with continual constraints of power efficiency and high-speed communication, particularly for portable devices, are among the main drivers of emerging research in next-generation mm-wave wireless communications topics such as 5G, WiGig, and E-band. Frequency-reconfigurable and linear transceivers are an attractive choice for these applications as they can enable high power efficiency with a high level of integration while supporting multi-GHz bandwidth.

Currently, We are investigating a highly energy- and spectral-efficient mm-Wave beamforming transceiver architecture. We propose to explore a new analog pre-distorted linear PA architecture which can improve the spectral efficiency by 2-fold while supporting high-order QAM signals with large channel bandwidth (i.e., 1GHz). Using this approach, the burden of external linearization techniques such as digital pre-distortion can be substantially reduced. Furthermore, we will introduce a new design paradigm into the design challenge associated with variable-gain LNA, and propose to investigate a combined LNA and VGA architecture with near-continually- stepped variable gain functionality. This approach can to reduce the power consumption and active area by 3-fold.

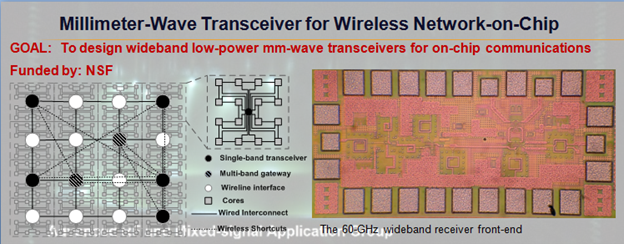

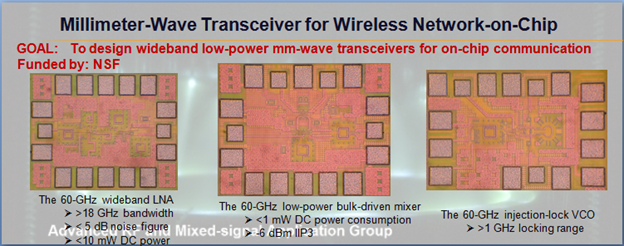

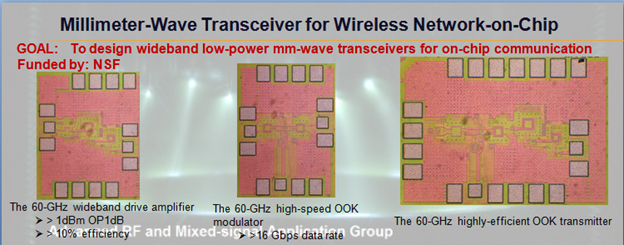

6. Millimeter-Wave Transceiver for Wireless Network-on-Chip

The objective of this research is to design millimeter-wave wireless transceivers that can handle the data rate of tens of Gb/s, while maintaining an energy efficiency of around 1 pJ/bit. Such a highly efficient wireless transceiver is an essential building block in the wireless network-on-chip (WiNoC) architecture. In future multi-core VLSIs that contain hundreds of cores, the conventional network-on-chip (NoC) architecture will not only consume a significant amount of power, but also entail multiple hops for data to transmit from one core to another. WiNoC is a competitive alternative which can provide direct one-hop links for distant cores. Moreover, to cope with the demand of “green” computing, we’re seeking innovative methodologies to reduce the power consumption of the mm-wave transceivers.

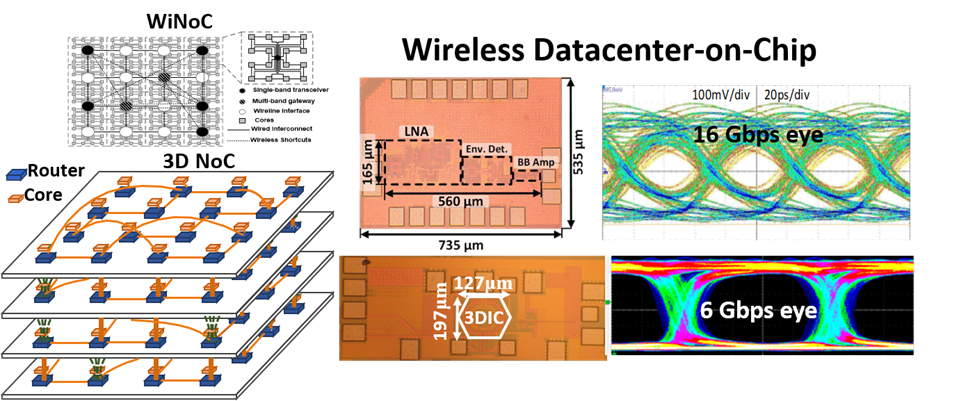

7. Wireless Datacenter-on-Chip (Wi-DoC)

This project introduces a new direction in networked system design enabled by the emerging wireless datacenter on-chip interconnect paradigm. To this end, the research goals include:

– Design of a small-world wireless network architecture as a communication backbone for manycore-enabled wireless data-center-on-chip (WiDoC)

– Design methods at the physical layer for highly-integrated 3D wireless DoC suitable for low latency data communication

This project enables on-chip communication via 3D small-world network architecture with sub-THZ wireless links in the planar layers and near field inductive coupling (NFIC)-based wireless interconnects in the vertical direction for complete reconfigurable architeture. Such platforms are suitable for big data applications with energy and area efficient architectures.

The project complements interdisciplinary concepts from network-on-chip (NoC), wireless, and complex networks, communication circuits, and optimization techniques aimed at single-chip solutions for achieving data center-scale performance.

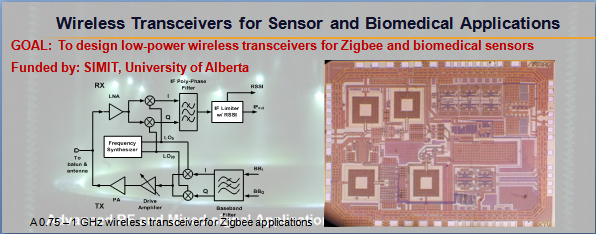

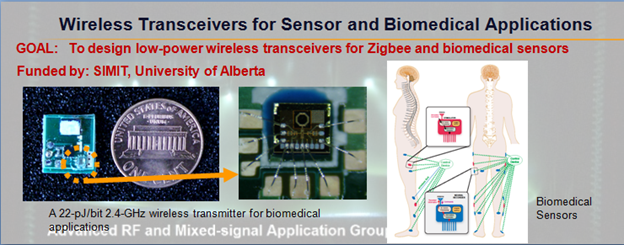

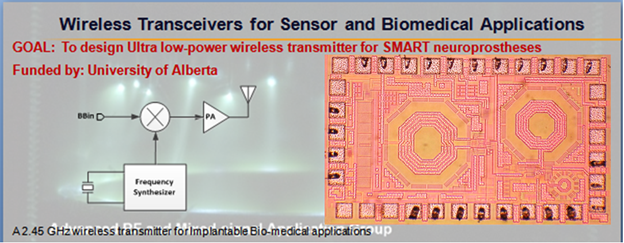

8. Biomedical Applications

The objective of this research is to design low-cost low-power wireless transceivers that are uniquely desirable in applications like industrial monitoring, home automation, and biomedical sensors. Long battery life and small form-factor are extremely crucial in those applications, especially for implantable sensors. Therefore, low-power designs at the architecture level, such as direct-conversion, injection-lock receivers, as well as in-circuit levels, e.g., body-enabled design, switchless RF front-end, and current-reuse techniques are being investigated.